# LIGA and its Application to Electrical Interconnects

# Rosenberger

**Frank Schonig**

Rosenberger, R&D

Jim Jaquette

Rosenberger, Program Mgmt.

## IEEE SW Test Workshop

Semiconductor Wafer Test Workshop

June 10 - 13, 2012 | San Diego, California

#### **Outline**

Brief introduction to Rosenberger (very brief)

Tutorial of the "UV LIGA Process"

Examples of parts produced with the "UV LIGA Process"

Electrical Interconnects produced with the "UV LIGA Process"

Challenges, Solutions, & Discoveries

What's next

http://en.wikipedia.org/wiki/LIGA

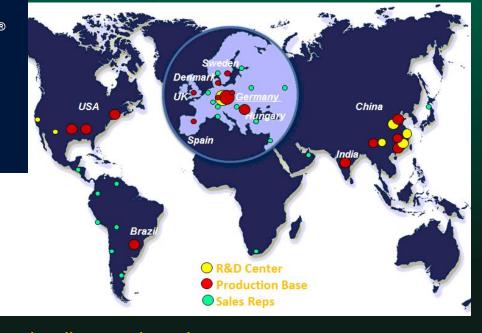

#### Rosenberger is a Global Engineering & Manufacturing Company

We are industry leaders in high frequency signal delivery

#### **Business Areas**

•Communication

RF-Coaxial Connectors

Rosenberger

•Communication SLink Site Solutions

•Test & Measurement

•Automotive FAKRA RosenbergerHSD®

Fiber Optics

12 Countries

18 Production facilities WW

~4900 Employees WW

Most process lines vertically integrated

Well known and respected as a leader in innovation in all served market segments

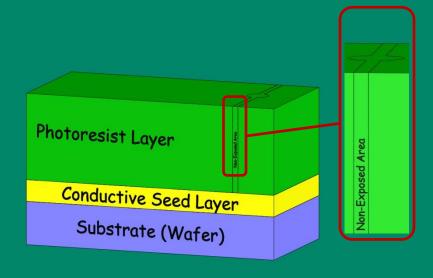

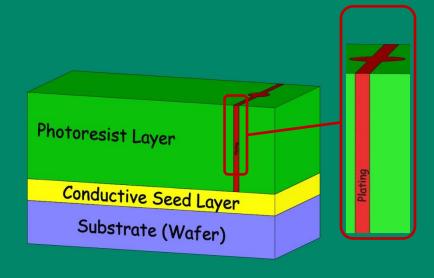

Wafer Prep  $\rightarrow$  Exposure  $\rightarrow$  Develop  $\rightarrow$  Plating  $\rightarrow$  Planarizing  $\rightarrow$  Etch  $\rightarrow$  Release

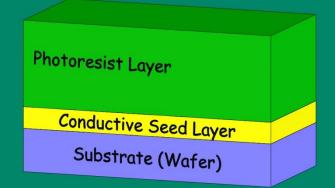

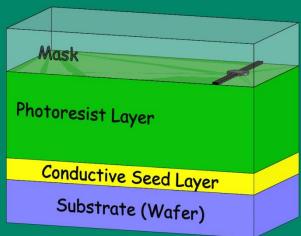

Substrate (Wafer)

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Conductive Seed Layer

Substrate (Wafer)

Conductive Seed Layer Applied with PVD Process

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Photoresist applied with Spin Coat Process

Wafer ready for processing

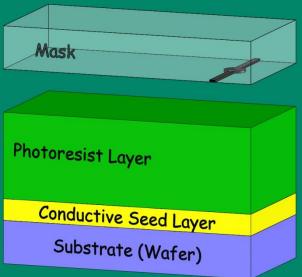

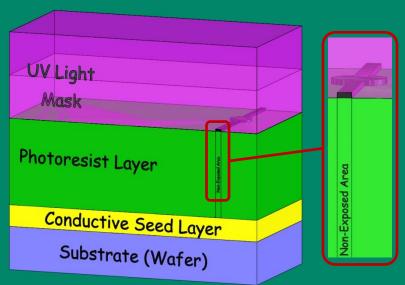

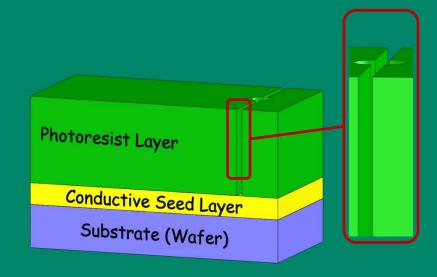

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

**Design and Procure Mask**

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Mask is Aligned to Wafer

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Exposed to a UV Light Source

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

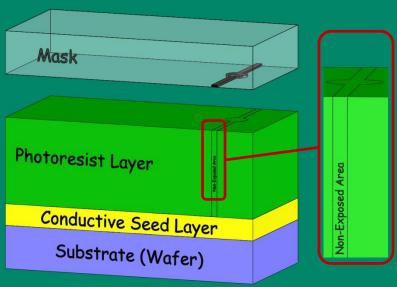

Mask Pattern is Transferred

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Photoresist Is cured In Curing Process

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Non-Exposed Photoresist Chemically Remove (Conductive layer now exposed)

Wafer can now be defined as a Mold

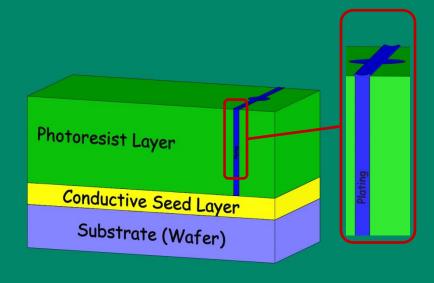

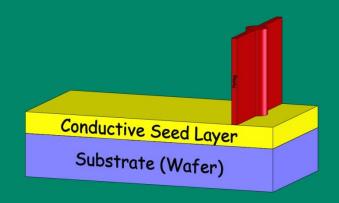

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Wafer is Plated

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

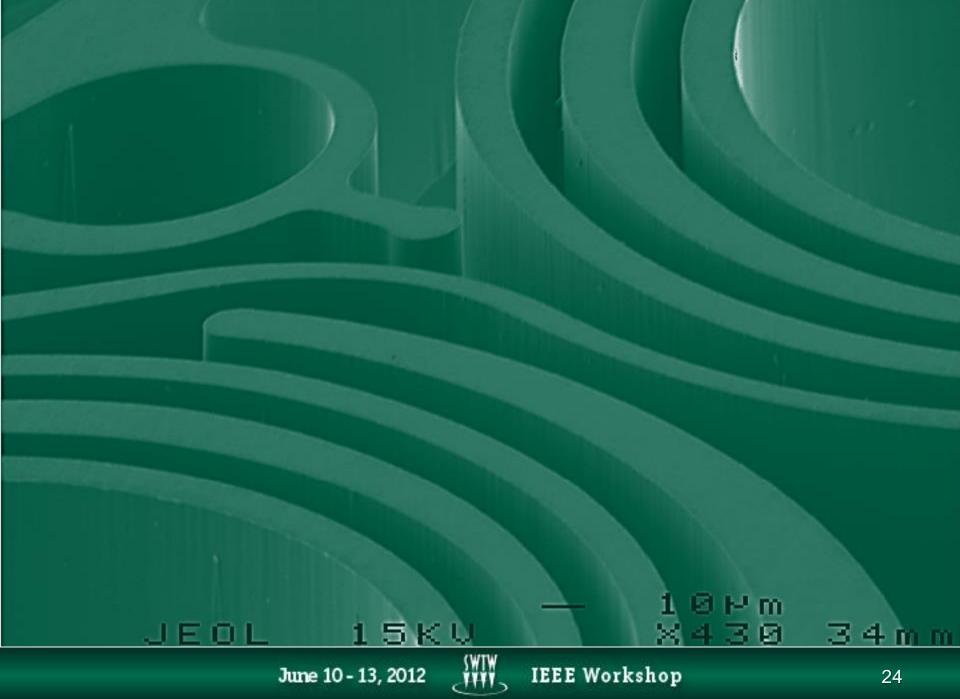

Wafer is Lapped to final thickness

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Photoresist Removed with Plasma Etch Process

Wafer Prep → Exposure → Develop → Plating → Planarizing → Etch → Release

Conductive Seed Layer Chemically Removed

Parts are released

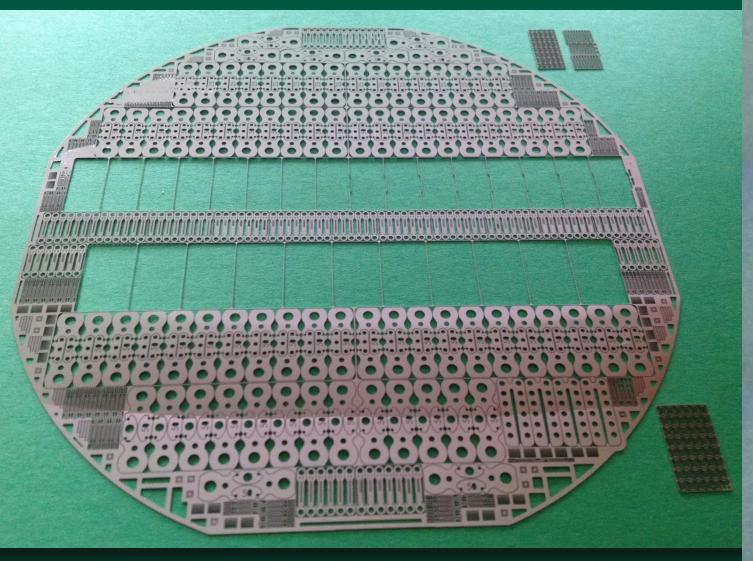

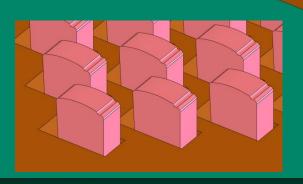

#### **Example of released wafer**

# **MCI** Materials

#### **Electroform** materials

Ni NiCo NiP NiFe

NiW

Au

AuNi

AuCo

Cu

Ag

Others...

#### Electroplate only materials

(<5µm)

Ru

Rh

Pd

W

And all of the Electroform list

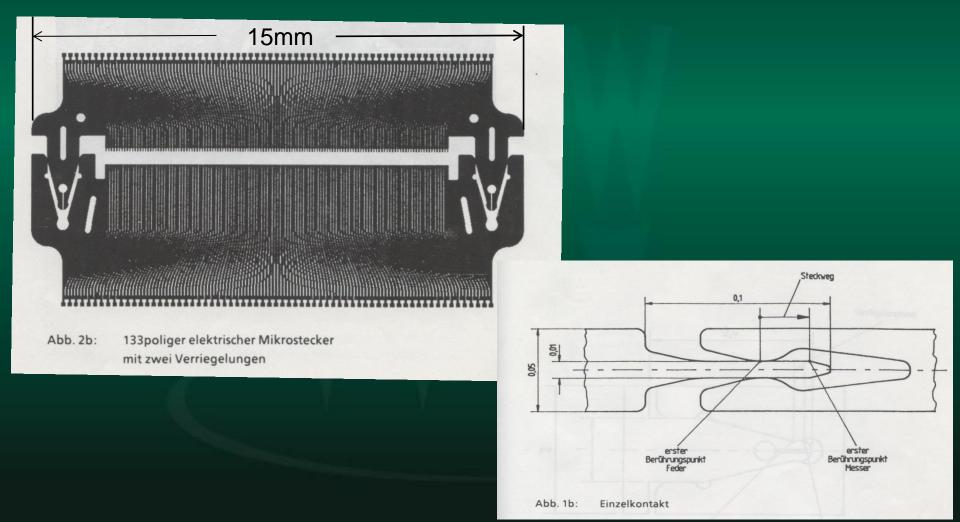

# **Commercialized LIGA Products**

## **Current Rosenberger LIGA Based Products**

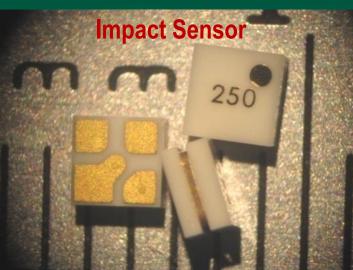

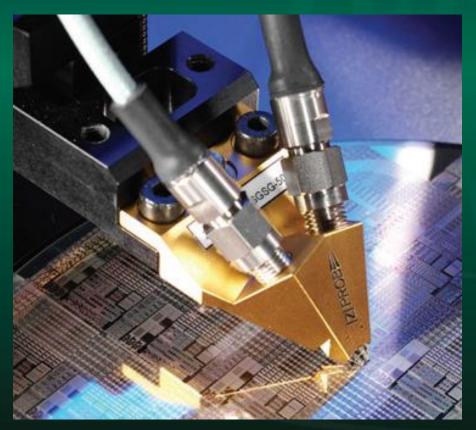

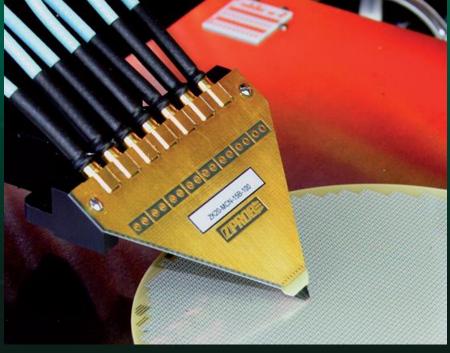

Exclusively developed for Suss MicroTec, now owned by Cascade Microtech Inc. (2000)

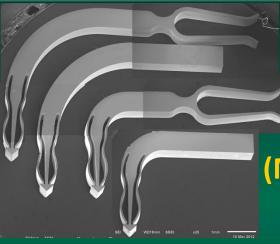

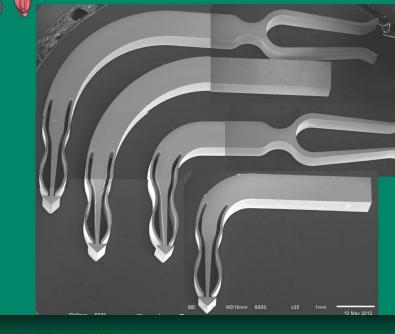

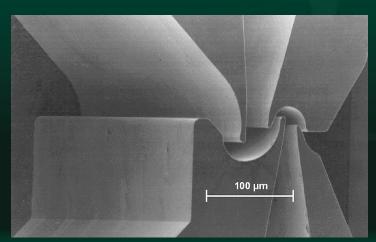

#### Cascade Microtech Z-Probe

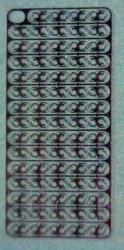

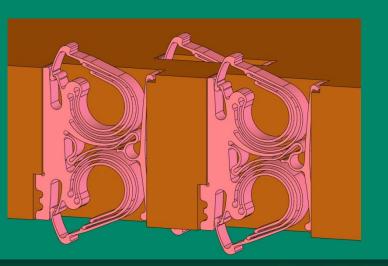

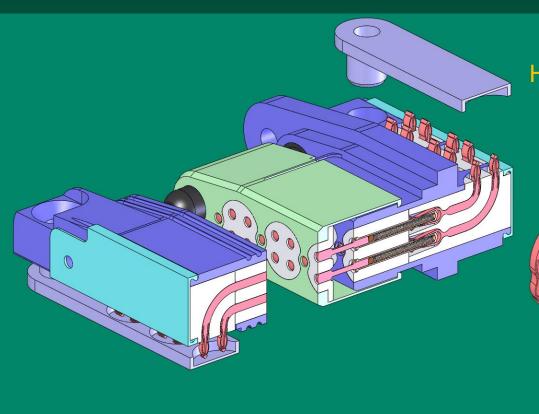

# Rosenberger MCI product line

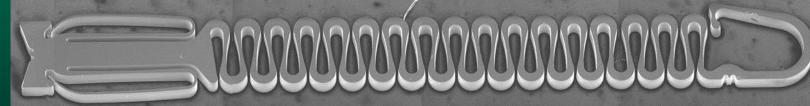

(Monolithic Compliant Interconnects)

MARRITARRARAMA

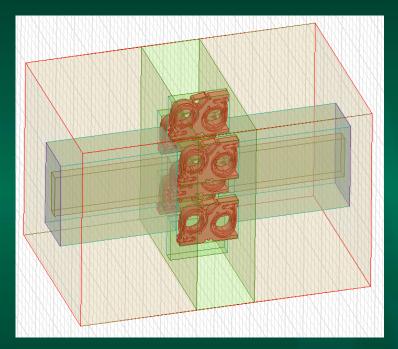

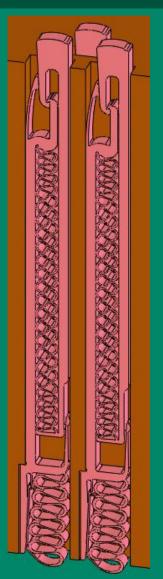

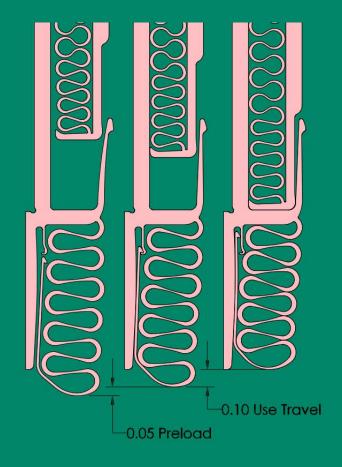

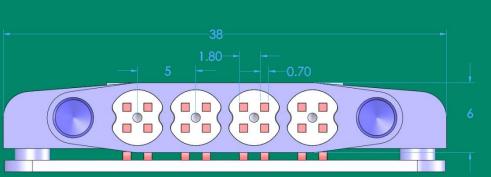

## **0.8mm Pitch Interposer Array**

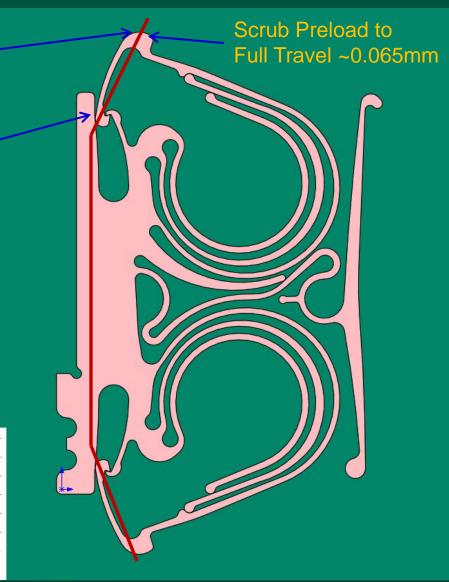

0.076mm Preload Per Side

0.15mm Usable Travel Per Side

0.30mm Total Usable Travel

0.150mm Thickness

0.065mm Contact to DUT Scrub Per Side

1.0mm Fully compressed Height

Total Travel is ~31% of Height

Targeted applications: MLC, MLO to PCB PCB-PCB **Test Sockets OEM Sockets**

Version

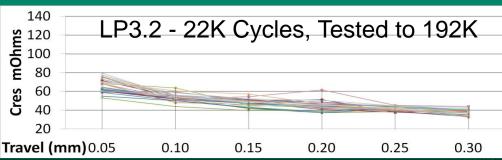

## **0.8mm Pitch Interposer Array**

Design Goals

Low Force √

Short/Direct Signal Path √

Scrub/Wipe at Contact Surfaces √

Low & Consistence CRES √ \*

Low Cost √ \*

Well Suited for HVM Automation

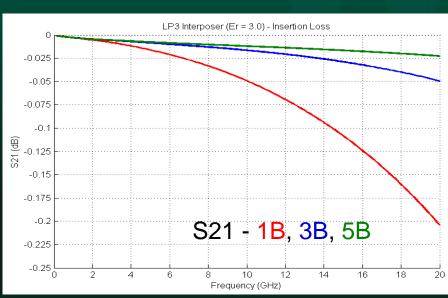

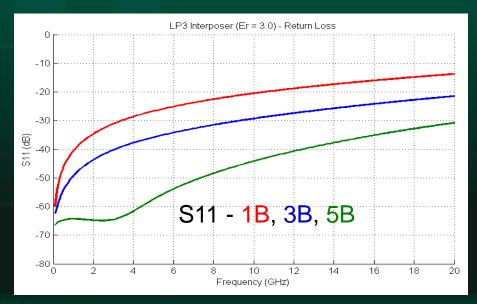

# 0.8mm Array Interposer Interconnect

The simulated SI data shown is in keeping with the standard industry practice of providing interconnect performance in use cases that can never be achieved by the end user in actual applications.

#### However in all fairness...

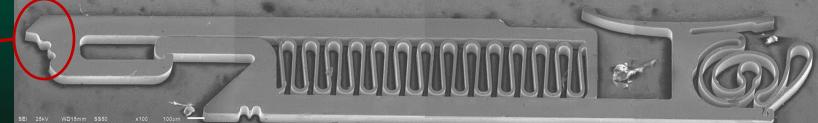

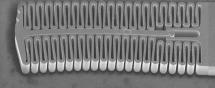

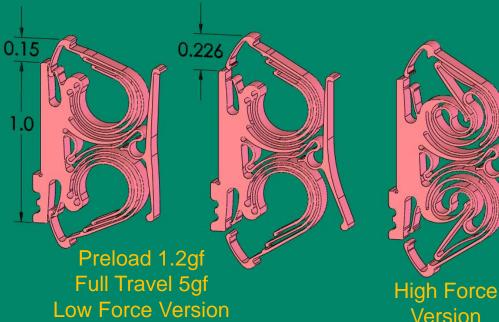

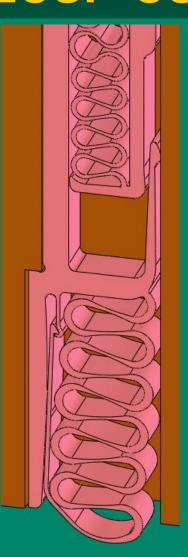

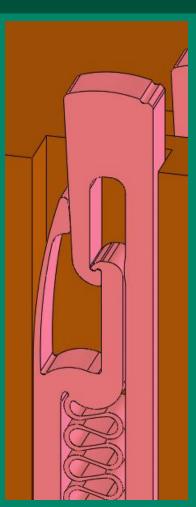

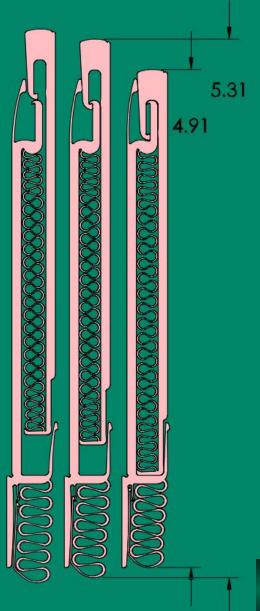

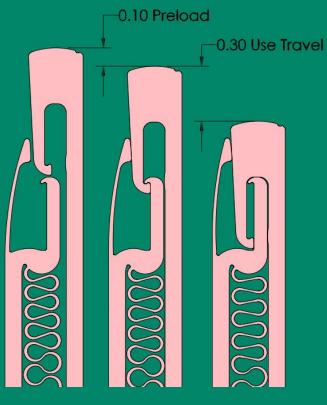

## WLCSP-CSP Interconnects (0.4 mm Shown)

**Design Goals** Low Force **Direct Signal Path** Scrub/Wipe at DUT Contact Surface Low & Consistent CRES **Low Cost HVM** Automation **Array Pitches** 0.8mm 0.4mm 0.3mm 0.2mm

# WLCSP-CSP Interconnects (0.4 mm Shown)

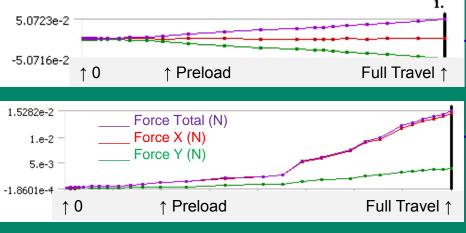

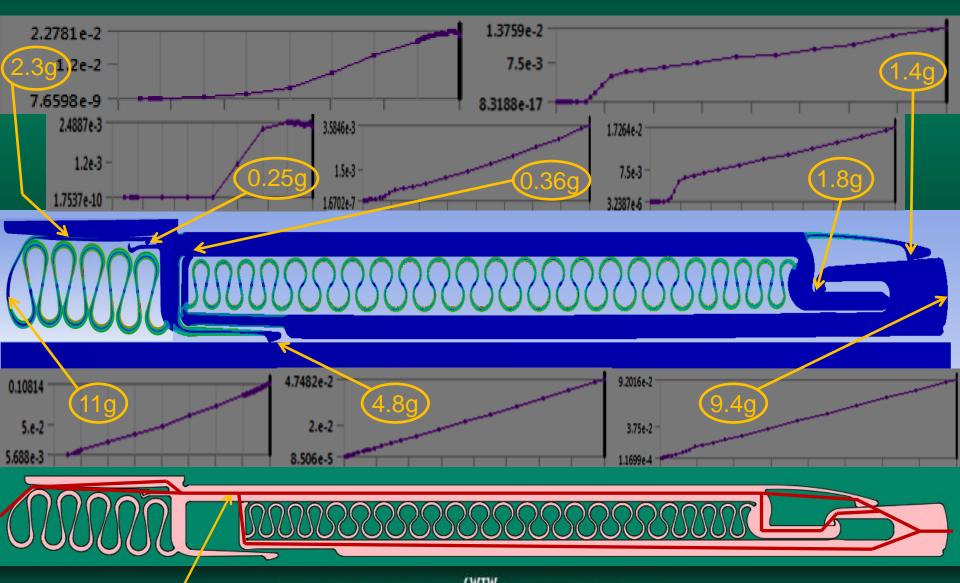

Preloaded 1gf, Full Travel 11gf

# WLCSP-CSP Interconnects (0.4 mm Shown)

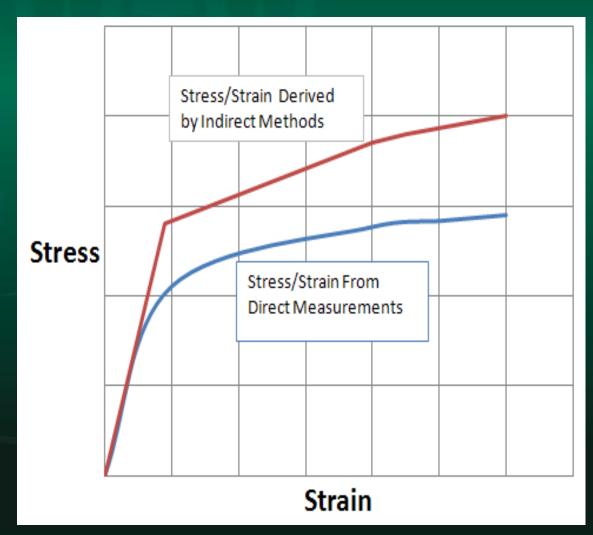

# Material Properties Expectations Vs. Reality

Common industry (LIGA) practice is for mechanical properties to be indirectly derived from failure data.

Current mechanical properties based on actual tests of micro samples.

Precise Yield stress is difficult to define.

There is no substitute for direct measurements...

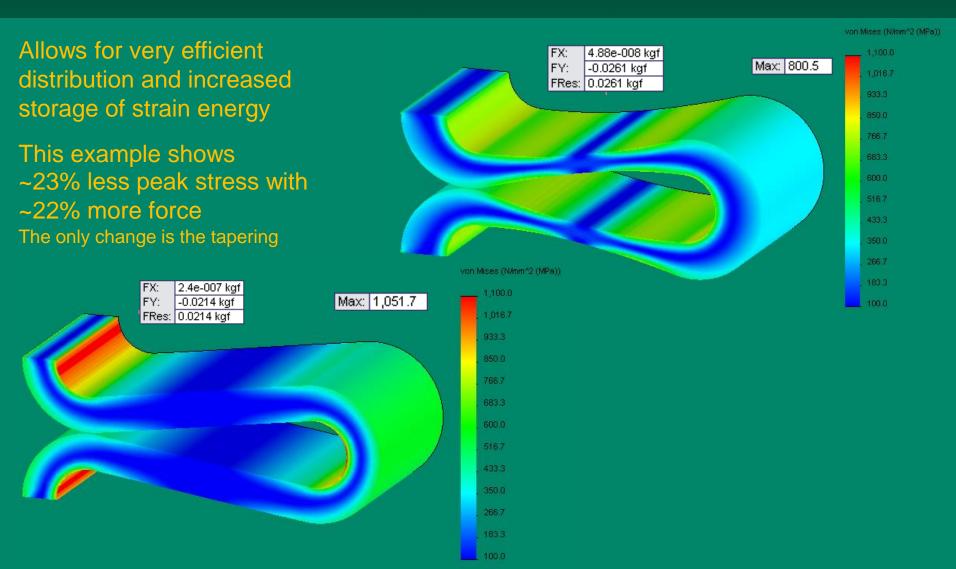

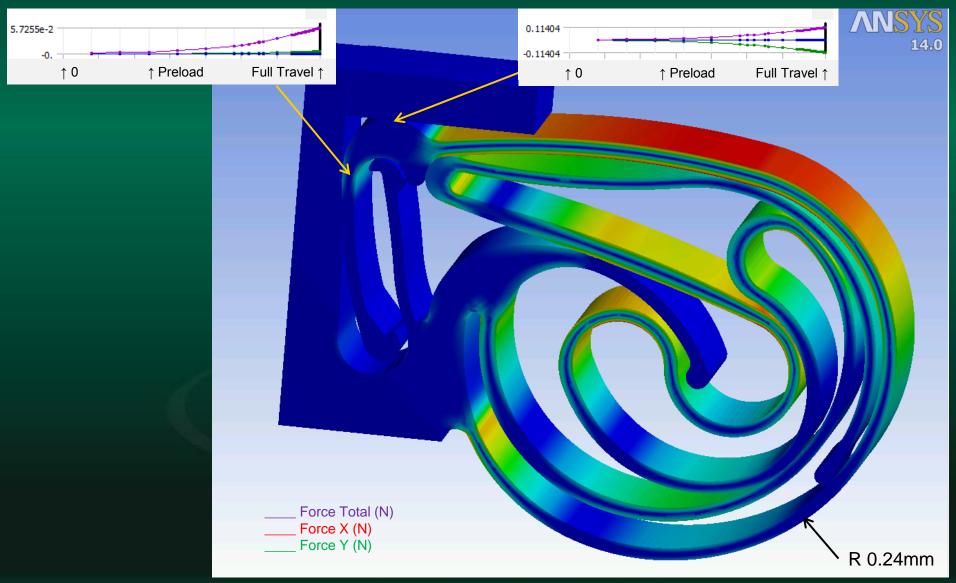

## Design Advantages: Energy Storage

# **Design Advantages: Flexibility**

# What's Important

(The critical links in the chain)

- ➤ Material Behavior

- ➤ Design Rules

- Process Knowledge & Stability

- > Imagination

- Preconceived notions

## **Design Advantages Prototype Flexibility**

An effective Prototype Process

HDMI & USB 3.0 Signals, and Power

-60db Isolation (EMI)

#### What if..., Could we...

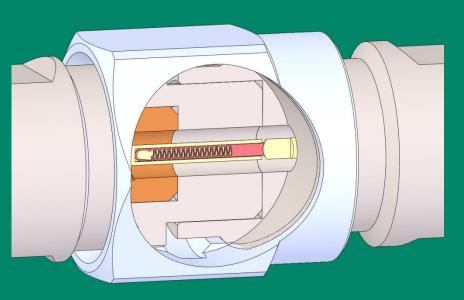

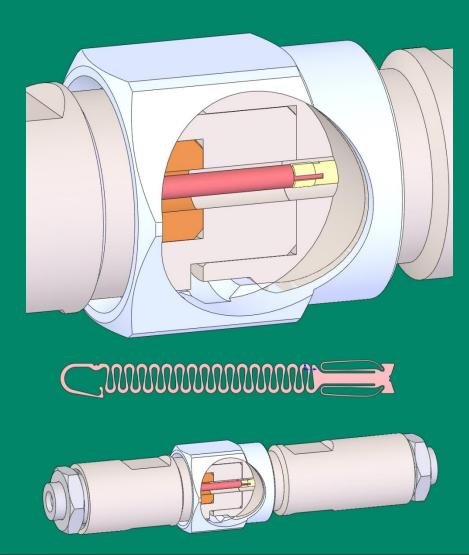

RPC-1.60 80Ghz Connector Typical Pin & Socket Signal interconnect

#### Can we:

Improve the mating cycles -Yes

Improve the robustness -Yes

Improve the cost -Yes

Maintain the Signal Integrity - Close but No

- ➤ What's Next? (quite a bit)

- Continued Reliability Testing & Characterization

- Continued Signal Integrity Characterization

- Beta Site Testing

- Surface Platings

- > Layering materials

- > Commercialization

- > Consumables

- > OEM

- ≥ 2<sup>nd</sup> source partnerships

- ➤ Will we sell loose Interconnects? yes

# **Appendix**

## **Our Development Team**

Bernhard Rosenberger CTO, Head of WW R&D (Germany)

Dr. Michael Wollitzer, Head of R&D (Germany)

Jim Jaquette MCI Program Manager (USA)

Roland Neuhauser MCI Project Manager, Factory liaison (Germany)

Steve Fahrner MCI Structual, Thermal, Material Analysist (USA)

**Trevor Mitchell MCI Signal Integrity Engineer (Germany)**

Michael Angerbauer Materials Test Engineer (Germany)

Florian Wohlschlager Reliabitily Test Engineer (Germany)

Frank Schonig MCI Designer, R&D (USA)

Hauke Schütt Business Unit Manager Test and Measurement (Germany)

Hans Rosenberger CEO (Germany) (The guy that pays for all this)

#### The LIGA Process

LIGA is a German acronym for: Lithographie, Galvanoformung, Abformung (Lithography, Electroplating, and Molding) a fabrication technology used to create high-aspect-ratio microstructures.

- > X-Ray LIGA is a fabrication process in micro-technology that was developed in the early 1980s.

- > X-Ray LIGA requires exposure to parallel beams of high-energy synchrotron radiation (X-rays)

- > UV LIGA utilizes an inexpensive ultraviolet light source

- > UV LIGA is much cheaper and more accessible than its X-ray counterpart.

- > UV LIGA is not as effective at producing precision molds as its X-ray counterpart.

- > UV LIGA is used when cost must be kept low and very high aspect ratios are not required.

The X-ray LIGA process was originally developed at the Forschungszentrum Karlsruhe, Germany, to produce nozzles for uranium enrichment.

http://en.wikipedia.org/wiki/LIGA

#### **LIGA X-Ray & UV Comparative Pros & Cons**

#### X-Ray LIGA Pros

- Extremely high aspect ratios 100:1

- Less processing risks compared to UV

- Cost efficient for wide range of Prototyping projects

#### > X-Ray LIGA Cons

- > limitations in beam width, practically speaking 4" wafers max (leads to misconception on cost)

- Availability to synchrotron beams limited to universities and government facilities

- > Synchrotron beams require noteworthy down time due to maintenance, both scheduled, and non-scheduled

#### UV LIGA Pros

- Currently available on 6" & 8" wafers (as with IC's it's a real estate business)

- Δ in Precision is in the Nano-meter range when compared to X-Ray

- Aspect ratios so far are not viewed as limitations

- Significantly less costly than other currently available and well know competing processes

#### UV LIGA Cons

Difficult to layer, generally accepted limit is 3 layers (thickness is not limited)

#### Where it all started for us

1991 Rosenberger, the German Government, and Forschungszentrum Karlsruhe, Germany